### SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# SC2021A Type-C/ PD and Dual DPDM Fast Charge Controller

## 1 Description

SC2021A is a Type-C / PD and DPDM fast charge controller. It complies with the latest Type-C and PD 3.0 standards and supports the proprietary high voltage fast charge protocols with dual DPDM interfaces. It targets for the wall adapters, travel adapters and car chargers.

SC2021A minimizes external components by integrating USB PD baseband PHY, Type-C detection, dual DPDM PHYs, VBUS discharging paths, VCONN supply, programmable feedback compensation, voltage and current sense, 10-bit high performance ADC, dual 10-bit DACs, NMOS gate driver, I2C interface and protection circuits. It contains a 32-bit high performance microcontroller core with 32kByte MTP ROM and 2.5kByte RAM, which provides cost effective solutions to many applications.

SC2021A supports various protection mechanisms including Over Voltage Protection (OVP), Under Voltage Protection (UVP), Over Current Protection (OCP), Short Circuit Protection (SCP), Over Temperature Protection (OTP), DPDM Over Voltage Protection (DPDM OVP), CC Over Voltage Protection (CCOVP), VCONN Over Voltage (VCONN OVP), VCONN OVP), VCONN OVP), VCONN OVP), VCONN OVP), vCONN OVP), so to effectively ensure stable and reliable operation of system.

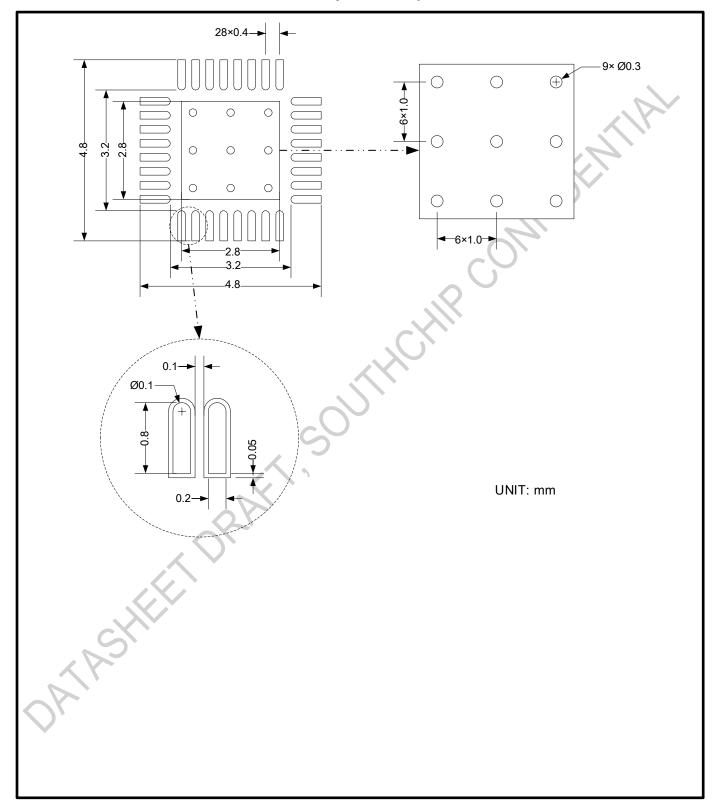

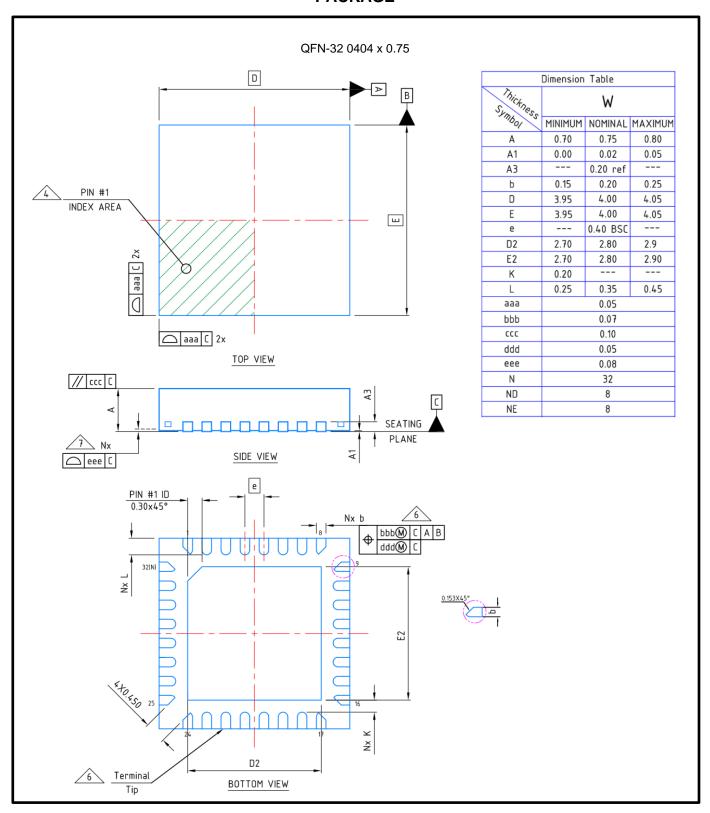

The SC2021A is available in 32-pin QFN package.

## 2 Features

#### USB Type-C

- Support Type-C DFP protocols

- Configurable resistor R<sub>P</sub>

#### USB Power Delivery

- > Support DFP USB PD 3.0 with PPS

- Hardware BMC transmitter and receiver

- > Full feature physical layer

- Hardware CRC

- Hardware reset

- Integrate PD 3.0 protocol engine

- Integrate VCONN and support SOP' for e-marker

## Dual DPDM Fast Charging Interfaces

- Integrate 2x firmware controlled DPDM interfaces

- Support Apple charging, BC1.2, DCP, HVDCP, FC, AFC, FCP, SCP, VOOC, UART, I2C and other proprietary charging protocols

### Power

- Wide operation range: 3.05V to 22V (26V tolerant)

- Integrate programmable feedback compensation

#### MCU Subsystem

Integrated 32-bit high performance MCU core

## 3 Applications

- Wall adapters

- Travel adapters

- Car chargers

- 32kByte MTP and 2.5kByte RAM

- > Reserve independent space for storing chip ID code

- Support UART, I2C and multiple I/Os

- Support sleep mode

## Analog Block

- Support OPTO interface for adapter

- Support FB interface for car charger

- Dual DACs for CC/CV loop.

- 10-bit ADC to monitor the voltage / current / DPDM/ other signals

- Integrated high side current sense amplifier

- Integrated NMOS gate driver

- Integrated VBUS discharging paths

- Integrated temperature sense module

### Protections

- 26V tolerant for CC1 and CC2

- 12V tolerant for DP and DM

- On chip OVP, UVP, SCP, VCONN OVP, VCONN OCP, VCONN SCP, OTP, DPDM OVP, CC OVP

#### Package

> 32-pin QFN, 4mm x 4mm x 0.75mm

## 4 Device Information

| Part Number | Package | Body Size          |

|-------------|---------|--------------------|

| SC2021AQDER | QFN32   | 4mm x 4mm x 0.75mm |

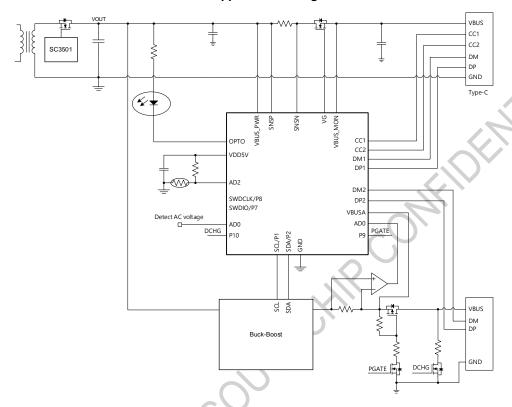

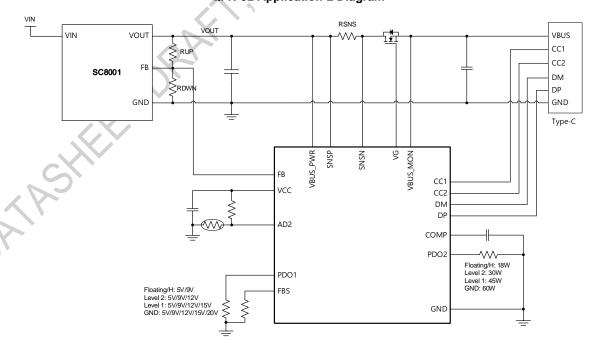

## 5 Typical Application Diagram

## QFN-32 Application-1 Diagram

## QFN-32 Application-2 Diagram

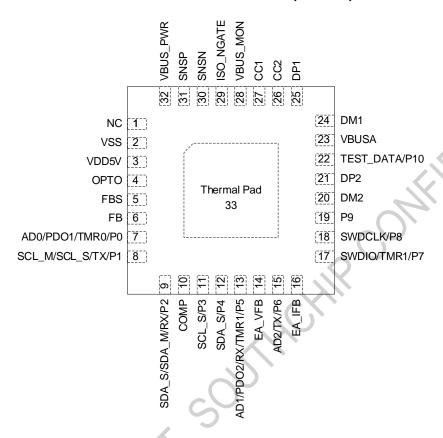

## 6 Terminal Configuration and Functions

## TOP VIEW of SC2021A (QFN-32)

| TERMINAL  NUMBER NAME |       | I/O | DESCRIPTION                                                                                                                                                                                                    |  |  |

|-----------------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                       |       | 10  | DESCRIPTION                                                                                                                                                                                                    |  |  |

| 1                     | NC    |     | No connect                                                                                                                                                                                                     |  |  |

| 2                     | VSS   | 1/0 | Ground of IC                                                                                                                                                                                                   |  |  |

| 3                     | VDD5V | 0   | Output of 5V LDO. Provide power supply for internal circuits. Connect a 2.2uF capacitor to ground                                                                                                              |  |  |

| 4                     | OPTO  | _   | Current sink output for optocoupler connection                                                                                                                                                                 |  |  |

| 5                     | FBS   | -   | This pin is used to set the bias current when FB control is used to adjust the output voltage of power IC. Connect a resistor between this pin and ground. Leave this pin floating if FB control is not used   |  |  |

| 6                     | FB    | _   | If FB control is adopted to adjust the output voltage of the power IC, connect this pin to the feedback divider of the power IC. If FB control is not adopted, leave this pin floating or use this pin as GPIO |  |  |

|                       | AD0   | I   | A/D converter input channel 0                                                                                                                                                                                  |  |  |

| 7                     | PDO1  | I   | Power data object setting pin1. Connect a resistor from this pin to ground for firmware setting the output voltage                                                                                             |  |  |

|    | TMR0   | 0   | Timer0 output. When configured as timer0 output, this pin shall toggle once timer0 counter counts to zero                    |

|----|--------|-----|------------------------------------------------------------------------------------------------------------------------------|

|    | P0     | I/O | General purpose IO                                                                                                           |

|    | SCL_M  | 0   | I2C master interface clock line                                                                                              |

| 0  | SCL_S  | 0   | I2C slave interface clock line                                                                                               |

| 8  | TX     | 0   | Transmit port when configure as UART interface                                                                               |

|    | P1     | I/O | General purpose IO                                                                                                           |

|    | SDA_M  | I/O | I2C master interface data line                                                                                               |

| 9  | SDA_S  | I/O | I2C slave interface data line                                                                                                |

| 9  | RX     | _   | Receive port when configure as UART interface                                                                                |

|    | P2     | I/O | General purpose IO                                                                                                           |

| 10 | COMP   | I/O | If FB control is adopted to adjust the output voltage of the power IC, connect a capacitor to this pin to compensate CC loop |

| 11 | SCL_S  | 1   | I2C slave interface clock                                                                                                    |

| 11 | P3     | I/O | General purpose IO                                                                                                           |

| 12 | SDA_S  | I/O | I2C slave interface data                                                                                                     |

| 12 | P4     | I/O | General purpose IO                                                                                                           |

|    | AD1    | _   | A/D converter input channel 0                                                                                                |

|    | PDO2   | _   | Power data object setting pin2. Connect a resistor from this pin to ground for firmware setting the output power             |

| 13 | RX     |     | Receive data in when configure as UART interface                                                                             |

|    | TMR1   | 0   | Timer1 output. When configured as timer1 output, this pin shall toggle once timer1 counter counts to zero                    |

|    | P5     | I/O | General purpose IO                                                                                                           |

| 14 | EA_VFB | I/O | Constant voltage loop EA compensation pin                                                                                    |

|    | AD2    | I   | A/D converter input channel 0                                                                                                |

| 15 | TX     | 0   | Transmit when configure as UART interface                                                                                    |

| ¥  | P6     | I/O | General purpose IO                                                                                                           |

| 16 | EA_IFB | I/O | Constant current loop EA compensation pin                                                                                    |

| 17 | SWDIO  | I/O | Debug data line                                                                                                              |

## **SC2021A DATASHEET DRAFT**

|    | TMR1        | 0   | Timer1 output. When configured as timer1 output, this pin shall toggle once timer1 counter counts to zero                                       |

|----|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

|    | P7          | I/O | General purpose IO                                                                                                                              |

| 40 | SWDCLK      | I   | Debug clock line                                                                                                                                |

| 18 | P8          | I/O | General purpose IO                                                                                                                              |

| 19 | P9          | I/O | General purpose IO                                                                                                                              |

| 20 | DM2         | I/O | DM line of fast charging interface 2                                                                                                            |

| 21 | DP2         | I/O | DP line of fast charging interface 2                                                                                                            |

| 22 | P10         | I/O | General purpose IO                                                                                                                              |

| 23 | VBUSA       | I   | Connected to the VBUS line of the USB-A port. It can discharge the output capacitor and could be used to sense VBUS voltage of USB-A port       |

| 24 | DM1         | I/O | DM line of fast charging interface 1                                                                                                            |

| 25 | DP1         | I/O | DP line of fast charging interface 1                                                                                                            |

| 26 | CC2         | I/O | Type-C configure channel2. It also supports VCONN output                                                                                        |

| 27 | CC1         | I/O | Type-C configure channel1. It also supports VCONN output                                                                                        |

| 28 | VBUS_MON    | 1   | Connected to the VBUS line of the USB Type-C port. It can discharge the output capacitor and could be used to sense VBUS voltage of Type-C port |

| 29 | NGATE       | 0   | Load switch (NMOS) driver                                                                                                                       |

| 30 | SNSN        | 1   | Negative input of the internal current sense amplifier. Connect to the high side current sense resistor for the Type-C port                     |

| 31 | SNSP        | 7   | Positive input of the internal current sense amplifier. Connect to the high side current sense resistor for the Type-C port                     |

| 32 | VBUS_PWR    | _   | IC supply input. It supports more than 100mA discharging capability for the internal VBUS capacitor and could be used to sense VBUS voltage     |

| 33 | Thermal Pad | -   | Connect this pad to VSS                                                                                                                         |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                          |                                                                                                                                                                                            | MIN  | MAX   | Unit |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|

|                          | ISO_NGATE                                                                                                                                                                                  | -0.3 | 31    | V    |

|                          | VBUS_PWR, VBUS_MON, SNSP, SNSN, CC1, CC2, OPTO, VBUSA                                                                                                                                      | -0.3 | 26    | V    |

| Voltage range at         | DP1, DM1, DP2, DM2                                                                                                                                                                         | -0.3 | 12    | V    |

| terminals <sup>(2)</sup> | FB, AD0/PD01/TMR0/P0, SCL_M/SCL_S/TX/P1, SDA_S/SDA_M/RX/P2, SCL_S/P3, SDA/P4, AD1/PD02/RX/TMR1/P5, AD2/TX/P6, SWDIO/TMR1/P7, SWDCLK/TEST_SCL/P8, P9, P10, VDD5V, COMP, EA_VFB, EA_IFB, FBS | -0.3 | 3 5.5 |      |

| TJ                       | Operating junction temperature range                                                                                                                                                       | -40  | 150   | °C   |

| T <sub>stg</sub>         | Storage temperature range                                                                                                                                                                  | -65  | 150   | °C   |

<sup>(1)</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 Thermal Information

| THERMAL RESISTA | THERMAL RESISTANCE (1)                 |     |      |  |

|-----------------|----------------------------------------|-----|------|--|

| $\theta_{JA}$   | Junction to ambient thermal resistance | TBD | °C/W |  |

| θ <sub>JC</sub> | Junction to case thermal resistance    | TBD | °C/W |  |

## 7.3 Handling Ratings

| PARAMETER          | DEFINITION                                                   |          | MIN  | MAX | UNIT |

|--------------------|--------------------------------------------------------------|----------|------|-----|------|

| ESD <sup>(1)</sup> | Human body model (HBM) ESD stress voltage <sup>(2)</sup>     | All pins | -2   | 2   | kV   |

| ESD                | Charged device model (CDM) ESD stress voltage <sup>(3)</sup> | All pins | -750 | 750 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

## 7.4 Recommended Operating Conditions

|                       |                                | MIN  | TYP | MAX                 | UNIT |

|-----------------------|--------------------------------|------|-----|---------------------|------|

| V <sub>BUS_PWR</sub>  | VBUS_PWR operation voltage     | 3.05 |     | 22                  | V    |

| C <sub>VBUS_PWR</sub> | Bulk capacitor at VBUS_PWR pin |      |     | 1600 <sup>(1)</sup> | μF   |

| C <sub>VBUS_MON</sub> | Bulk capacitor at VBUS_MON pin | 1    |     | 10                  | μF   |

| C <sub>VDD5V</sub>    | Capacitor at VDD5V pin         | 2.2  |     |                     | μF   |

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## SC2021A DATASHEET DRAFT

SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

| It is recommended to add external discharge circuit on VBUS_PWR, if the bulk capacitance at VBUS_PWR node is higher than 1600µF. | T <sub>J</sub> Operating junction temperature -40 125 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R <sub>SNS</sub>     | Sense resistor between CS+ and CS- pins                                  | 3   | 5        | 10  | mΩ |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------|-----|----------|-----|----|

| It is recommended to add external discharge circuit on VBUS_PWR, if the bulk capacitance at VBUS_PWR node is higher than 1600µF. | It is recommended to add external discharge circuit on VBUS_PWR, if the bulk capacitance at VBUS_PWR node is higher than 1600μF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | T <sub>A</sub>       | Operating ambient temperature                                            | -40 |          | 85  | °C |

| ORAFT, SOUTHICHIP CONFIDENTIAL SOUTHICHIP                                                                                        | ORAFI SOUTHCHIP CONTINUE OF THE CONTINUE OF TH | T <sub>J</sub>       | Operating junction temperature                                           | -40 |          | 125 | °C |

|                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (1) It is recommende | d to add external discharge circuit on VBUS_PWR, if the bulk capacitance |     | PWR node |     |    |

## 7.5 Electrical Characteristics

T<sub>J</sub>= 25°C unless otherwise noted.

| PARAMETER                 |                                   | TEST CONDITIONS                                                                                  | MIN  | TYP  | MAX  | UNIT |

|---------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY VOL                | TAGE                              |                                                                                                  |      |      |      |      |

| V <sub>BUS_PWR</sub>      | VBUS_PWR supply range             |                                                                                                  | 3.05 |      | 22   | V    |

| V <sub>BUS_PWR_POR</sub>  | VBUS_PWR power on threshold       | VBUS_PWR rising threshold                                                                        |      | 2.9  | 3.05 | V    |

| V <sub>BUS_PWR_UVLO</sub> | VBUS_PWR UVLO threshold           | VBUS_PWR falling threshold                                                                       | 2.55 | 2.7  |      | V    |

| I <sub>q_ACT</sub>        | Quiescent current in active mode  | VBUS_PWR=5V, MCU core is active                                                                  |      | 12   |      | mA   |

| I <sub>q_</sub> SBY       | Quiescent current in standby mode | VBUS_PWR=5V, standby<br>mode, digital DPDM module<br>wakes up, all analog<br>peripherals enabled | 0,   | 2    |      | mA   |

| I <sub>q_SLEEP</sub>      | Quiescent current in sleep mode   | Control loop disabled, MCU and peripherals all disabled except CC                                |      | 160  | 200  | μA   |

| 5V LDO                    |                                   |                                                                                                  |      |      |      |      |

| V <sub>LDO_5V</sub>       | 5V LDO regulation voltage         | VBUS_PWR = 5.5V~20V                                                                              | 4.9  | 5    | 5.1  | V    |

| V <sub>LDO_DROP</sub>     | 5V LDO drop out voltage           | V <sub>BUS_PWR</sub> -V <sub>LDQ5V</sub> , I <sub>OUT</sub> = 50 mA                              |      |      | 150  | mV   |

| I <sub>LDO_LIMIT</sub>    | LDO current limit                 | V <sub>BUS_PWR</sub> = 5V                                                                        | 90   | 100  | 120  | mA   |

| DISCHARGE                 |                                   | 60                                                                                               |      |      |      |      |

| IDIS_VBUS_PWR             | Discharging current at VBUS_PWR   | Register-Programmable                                                                            | 25   |      | 150  | mA   |

| RDCHG_VBUS_M<br>ON        | Discharging resistor at VBUS_MON  | b                                                                                                |      | 1    | 1.4  | kΩ   |

| RDCHG_VBUSA               | Discharging resistor at VBUSA     |                                                                                                  |      | 1    | 1.4  | kΩ   |

| NMOS GATE                 | DRIVER                            |                                                                                                  |      |      |      |      |

| $V_{DRV}$                 | Driving voltage                   | V <sub>GATE</sub> -V <sub>BUS</sub> MON, VBUS_PWR ≥ 3.3V                                         |      | 5    |      | V    |

| V <sub>CLAMP_GS</sub>     | Driver clamp voltage              | Vgate-Vbus_mon                                                                                   |      | 7    |      | V    |

| RDRIVE_UP                 | Driver pull up resistance         | VBUS_PWR=5V, Register-<br>Programmable                                                           | 20   |      | 200  | kΩ   |

| CURRENT SE                | NSE                               |                                                                                                  |      |      |      |      |

|                           | Coin of ourrent cance amplifier   | cs_sel_20x = 1                                                                                   | 19.8 | 20   | 20.2 |      |

| Gcsns                     | Gain of current sense amplifier   | cs_sel_20x = 0                                                                                   | 39.6 | 40   | 40.4 |      |

| Vocp                      | OCP threshold, calculated as      | cs_sel_vocp = 1                                                                                  |      | 30   | 31   | mV   |

| VOCP                      | IBUS*RSNS                         | cs_sel_vocp = 0                                                                                  |      | 36   | 37   | mV   |

| V <sub>OCP_DT</sub>       | OCP deglitch time                 |                                                                                                  |      | 1000 |      | μs   |

| GLINE_COMP                |                                   | cs_ana_comp_clamp_dis = 1                                                                        |      | 0    |      |      |

|                                            |                                                                  | cs_ana_comp_clamp_dis = 0,<br>cs_ana_comp_slop = 00b |       | 1/4    |       |      |

|--------------------------------------------|------------------------------------------------------------------|------------------------------------------------------|-------|--------|-------|------|

|                                            | VBUS output compensation                                         | cs_ana_comp_clamp_dis = 0,                           |       | 1/2    |       |      |

|                                            | VBUS output compensation respect to the output of CSNS amplifier | cs_ana_comp_slop = 01b<br>cs_ana_comp_clamp_dis = 0, |       | 7/12   |       |      |

|                                            |                                                                  | cs_ana_comp_slop = 10b                               |       | 7/12   |       |      |

|                                            |                                                                  | cs_ana_comp_clamp_dis = 0,<br>cs_ana_comp_slop = 11b |       | 5/6    |       |      |

| VLINE_COMP_MA                              | Max VBUS output voltage compensation                             |                                                      | 160   | 200    | 240   | mV   |

| ADC                                        |                                                                  |                                                      |       |        |       |      |

| V <sub>ADC_REF</sub>                       | Reference voltage for ADC                                        |                                                      | 2.249 | 2.253  | 2.257 | V    |

| N <sub>ADC</sub>                           | Resolution                                                       |                                                      |       | 10     |       | Bits |

|                                            |                                                                  |                                                      | 47.5  | 50     | 52.5  | ksps |

| D                                          | ADC comple rate                                                  | Register programable                                 | 23.75 | 25     | 26.25 | ksps |

| R <sub>SAMPLE</sub>                        | ADC sample rate                                                  | Register programable                                 | 9.5   | 10     | 10.5  | ksps |

|                                            |                                                                  | CX,                                                  | 4.75  | 5      | 5.25  | ksps |

| KADC_VBUS_PWR                              | Ratio from VBUS_PWR voltage sense                                |                                                      |       | 1/10   |       |      |

| K <sub>ADC_VBUS_MON</sub>                  | Ratio from VBUS_MON voltage sense                                | 9),                                                  |       | 1/10   |       |      |

| Kadc_vbusa                                 | Ratio from VBUSA voltage sense                                   | S                                                    |       | 1/10   |       |      |

| Kadc_csns                                  | Ratio from the output of current sense amplifier                 | 1                                                    |       | 1      |       |      |

| K <sub>ADC_DPDM</sub>                      | Ratio from DP1, DP2, DM1, DM2                                    |                                                      |       | 1/4    |       |      |

| K <sub>ADC_VDD5V</sub>                     | Ratio from VDD5V                                                 |                                                      |       | 1/4    |       |      |

| KADC_0_2                                   | Ratio from ADC0, ADC1 or ADC2 voltage sense                      |                                                      |       | 1      |       |      |

| Кітс                                       | Internal temperature sense coefficient                           |                                                      |       | 2.819  |       | mV/℃ |

| VITC_27°c                                  | Internal temperature sense output at 27 ℃                        |                                                      |       | 733.94 |       | mV   |

|                                            | Range                                                            |                                                      | 3.0   |        | 22.46 | V    |

| ADCVBUS_PWR,                               | LSB                                                              |                                                      |       | 22     |       | mV   |

| ADCVBUS_MON, ADCVBUSA                      | Error                                                            | VBUS = 3.3V ~ 9V                                     | -50   |        | 50    | mV   |

|                                            | Error                                                            | VBUS = 9V ~ 21V                                      | -100  |        | 100   | mV   |

|                                            | Range                                                            |                                                      | 0     |        | 8.983 | V    |

| ADC <sub>DPX</sub> ,<br>ADC <sub>DMX</sub> | LSB                                                              |                                                      |       | 8.78   |       | mV   |

| . ID ODIVIA                                | Error                                                            | Full range                                           | -150  |        | 150   | mV   |

| LSB   2.2                                                                                                                                                                                                                                                                                            | 5<br>1.0<br>1.0 | mV<br>mV<br>LSB<br>LSB |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------|

| Error         Full range         -5           INL         Integral non-linearity         -1.0           DNL         Differential non-linearity         -1.0           OPTO CV-DAC and CC-DAC           RFB_VBUS_PWR         VBUS_PWR Divider Resistance         RUP + RDWN on VBUS_PWR pin         2 | 1.0             | LSB<br>LSB             |

| DNL Differential non-linearity -1.0  OPTO CV-DAC and CC-DAC  RFB_VBUS_PWR VBUS_PWR Divider Resistance Rup + RDWN on VBUS_PWR pin 2                                                                                                                                                                   |                 | LSB                    |

| OPTO CV-DAC and CC-DAC  RFB_VBUS_PWR VBUS_PWR Divider Resistance Rup + Rown on VBUS_PWR pin 2                                                                                                                                                                                                        | 1.0             |                        |

| RFB_VBUS_PWR VBUS_PWR Divider Resistance Rup + RDWN on VBUS_PWR pin 2                                                                                                                                                                                                                                |                 | MΩ                     |

|                                                                                                                                                                                                                                                                                                      |                 | МΩ                     |

| Detic from VDIIC DMD to the Detic from VDIIC DMD to the                                                                                                                                                                                                                                              | 19              |                        |

| Ratio from VBUS_PWR to the input of ADC.  Ratio from VBUS_PWR to the input of ADC                                                                                                                                                                                                                    |                 |                        |

| NDAC_CV CV loop VREF resolution 10                                                                                                                                                                                                                                                                   | ) ~             | Bits                   |

| V <sub>BUS_PWR_ADJ_RANG</sub> VBUS_PWR adjust range [1] 2                                                                                                                                                                                                                                            | 22.46           | V                      |

| VBUS_PWR_STEP _VBUS_PWR adjust voltage per step 20                                                                                                                                                                                                                                                   |                 | mV                     |

| VDAC_ZERO_VOL T VBUS_PWR voltage at VDAC code = 0 [1] 1960 2000                                                                                                                                                                                                                                      | 2040            | mV                     |

| N <sub>DAC_CC</sub> CC loop I <sub>REF</sub> resolution 10                                                                                                                                                                                                                                           |                 | Bits                   |

| V <sub>REF_IDAC</sub> IDAC reference voltage 1.2                                                                                                                                                                                                                                                     |                 | V                      |

| V <sub>REF_IDAC_STEP</sub> IDAC step voltage 1.172                                                                                                                                                                                                                                                   |                 | mV                     |

| I <sub>REG_STEP</sub> Current regulation per step RSNS=5mΩ, GSNS = $40 \times$ 5.86                                                                                                                                                                                                                  |                 | mA                     |

| I <sub>VFB</sub> Current capability from VFB pin -16                                                                                                                                                                                                                                                 | 16              | μA                     |

| I <sub>IFB</sub> Current capability from IFB pin -16                                                                                                                                                                                                                                                 | 16              | μΑ                     |

| I <sub>OPTO</sub> OPTO control loop current 2                                                                                                                                                                                                                                                        |                 | mA                     |

| FB CV-DAC AND CC-DAC                                                                                                                                                                                                                                                                                 |                 |                        |

| V <sub>FB_VDAC_REF</sub> FB regulator VDAC reference 1.024                                                                                                                                                                                                                                           |                 | V                      |

| V <sub>FB_VDAC_STEP</sub> FB VDAC step voltage 1                                                                                                                                                                                                                                                     |                 | mV                     |

| $V_{BUS\_PWR\_STEP}_{_{VOLT\_FB}}$ $VBUS\_PWR$ adjust voltage per step via FB $R_{UP} = 20 \times R_{FBS}$ 20                                                                                                                                                                                        |                 | mV                     |

| IFB_SRCFB source capabilityFB = 2.5V400                                                                                                                                                                                                                                                              |                 | μΑ                     |

| $I_{FB\_SNK}$ FB sink capability FB = 0.8V 400                                                                                                                                                                                                                                                       |                 | μΑ                     |

| VDCDC_IDAC_RE F DCDC regulator IDAC reference 2.244 2.248                                                                                                                                                                                                                                            | 2.252           | mV                     |

| IFB_REG_STEP     Output current regulation per step by DCDC IDAC     10.98                                                                                                                                                                                                                           |                 | mA                     |

| ICOMP Current capability from COMP oin -4                                                                                                                                                                                                                                                            | 2               | μA                     |

| VBUS OVP and UVP                                                                                                                                                                                                                                                                                     |                 |                        |

| VBUS_PWR_OVP VBUS_PWR OVP rising fb_sel_uvp_th = 01b 105 110                                                                                                                                                                                                                                         | 115             | %                      |

| threshold fb_sel_uvp_th = 10b 110 115                                                                                                                                                                                                                                                                | 121             | %                      |

|                             |                                                            | fb_sel_uvp_th = 11b     | 115   | 120  | 125   | %  |

|-----------------------------|------------------------------------------------------------|-------------------------|-------|------|-------|----|

| V <sub>BUS_OVP_HYS</sub>    | VBUS_PWR OVP threshold hysteresis, respect to VDAC setting |                         |       | 0    | 5     | %  |

| typus pwp ovp               | VBUS_PWR over-voltage                                      | ovp_dgl_sel = 0         |       | 4    |       | μs |

| tvbus_pwr_ovp               | deglitch time                                              | ovp_dgl_sel = 1         |       | 40   |       | μs |

|                             |                                                            | fb_sel_uvp_th = 01b     | 73    | 75   | 77    | %  |

| $V_{\text{BUS\_PWR\_UVP}}$  | VBUS_PWR UVP falling threshold                             | fb_sel_uvp_th = 10b     | 82    | 85   | 88    | %  |

|                             |                                                            | fb_sel_uvp_th = 11b     | 91    | 95   | 99    | %  |

| V <sub>BUS_UVP_HYS</sub>    | VBUS_PWR UVP threshold hysteresis, respect to VDAC setting |                         |       | 0    | 3     | %  |

| tvbus_pwr_ovp               | UVP deglitch time                                          | uvp_dgl_sel = 0         |       | 4    |       | μs |

| TVBUS_PWR_OVP               | OVI degitori time                                          | uvp_dgl_sel = 1         |       | 40   |       | μs |

| $V_{\text{BUS\_SCP\_TH}}$   | VBUS_PWR SCP threshold                                     | .0                      | 3.1   | 3.2  |       | V  |

| tvmon_scp                   | VBUS_MON SCP deglitch time                                 |                         |       | 0    |       | μs |

| TYPE-C/ PD P                | ROTOCOLS                                                   |                         |       |      |       |    |

| I <sub>CC_80μ</sub> A       | CC1/2 pull up current                                      | CSRC_I = 00b            | 64    | 80   | 96    | μΑ |

| ICC_180µA                   | CC1/2 pull up current                                      | CSRC_I = 01b            | 165.6 | 180  | 194.4 | μΑ |

| ICC_330µA                   | CC1/2 pull up current                                      | CSRC_I = 10b            | 303.6 | 330  | 356.4 | μΑ |

| Rcc_open                    | CC1/2 open impedance                                       | CC1/2 in disable status | 126   |      |       | kΩ |

| VCC_0P2_th_src              | CC1/2 0.2V comparison threshold                            | CC1/2 as source         | 0.15  | 0.2  | 0.25  | V  |

| VCC_0P4_th_src              | CC1/2 0.4V comparison threshold                            | CC1/2 as source         | 0.35  | 0.4  | 0.45  | V  |

| VCC_0P66_th_src             | CC1/2 0.66V comparison threshold                           | CC1/2 as source         | 0.61  | 0.66 | 0.7   | V  |

| VCC_0P8_th_src              | CC1/2 0.8V comparison threshold                            | CC1/2 as source         | 0.75  | 0.8  | 0.85  | V  |

| V <sub>CC_1P23_th_src</sub> | CC1/2 1.23V comparison threshold                           | CC1/2 as source         | 1.18  | 1.23 | 1.28  | V  |

| VCC_1P6_th_src              | CC1/2 1.6V comparison threshold                            | CC1/2 as source         | 1.5   | 1.6  | 1.65  | V  |

| VCC_2P6_th_src              | CC1/2 2.6V comparison threshold                            | CC1/2 as source         | 2.45  | 2.6  | 2.75  | V  |

| V <sub>TH_CCOVP_RISI</sub>  | CCx OVP detection                                          | CCOVP rising threshold  |       | 7.2  |       | V  |

| V <sub>TH_CCOVP_FAL</sub>   | CCx OVP release                                            | CCOVP falling threshold |       | 7.0  |       | V  |

| Z <sub>Driver</sub>         | PD data Tx output impedance                                |                         | 33    |      | 75    | Ω  |

| Vswing                  | High level voltage for CC PD data          |                                                        | 1.05 | 1.125 | 1.2  | V  |

|-------------------------|--------------------------------------------|--------------------------------------------------------|------|-------|------|----|

| VCONN SWIT              | СН                                         |                                                        |      |       |      |    |

| V <sub>VCONN</sub>      | VCONN input voltage                        |                                                        | 3    |       | 5.5  | V  |

| R <sub>VCONN</sub>      | VCONN switch on resistance                 | LV ≥ 3.3V                                              |      |       | 40   | Ω  |

| I <sub>VCONN</sub>      | VCONN current capability                   | VBUS_PWR = 5V                                          |      | 50    |      | mA |

| I <sub>VCONN_OCP</sub>  | VCONN over current                         | Rising threshold                                       |      | 70    |      | mA |

| DPDM PROTO              | OCOL INTERFACES                            |                                                        |      |       | 1    |    |

| RSHORT                  | DP DM short resistance                     | VBUS_PWR = 5V ~ 21V                                    |      |       | 40   | Ω  |

| V <sub>3.3V</sub>       | DPDM 3.3V buffer output voltage            | VBUS_PWR = 5V ~ 21V                                    | 3.2  | 3.3   | 3.4  | V  |

| V <sub>2.7</sub> V      | DPDM 2.7V buffer output voltage            | VBUS_PWR = 5V ~ 21V                                    | 2.6  | 2.7   | 2.8  | V  |

| V <sub>1.96</sub> V     | DPDM 1.96V buffer output voltage           | VBUS_PWR = 5V ~ 21V                                    | 1.9  | 2     | 2.1  | V  |

| V <sub>TH_3V</sub>      | VTH3V comparator threshold at DPDM pin     | VBUS_PWR = 5V ~ 21V                                    | 2.9  | 3     | 3.1  | V  |

| V <sub>TH_2.2V</sub>    | VTH2.2V comparator threshold at DPDM pin   | VBUS_PWR = 3.3V ~ 21V                                  | 2.1  | 2.2   | 2.3  | V  |

| V <sub>TH_1.35</sub> V  | VTH1.35V comparator threshold at DPDM pin  | VBUS_PWR = 3.3V ~ 21V                                  | 1.25 | 1.35  | 1.45 | V  |

| V <sub>TH_0.425V</sub>  | VTH0.425V comparator threshold at DPDM pin | VBUS_PWR = 3.3V ~ 21V                                  | 0.35 | 0.425 | 0.5  | V  |

| V <sub>TH_0.325</sub> V | VTH0.325V comparator threshold at DPDM pin | VBUS_PWR = 3.3V ~ 21V                                  | 0.25 | 0.325 | 0.4  | V  |

| Rout_30k                | Output resistance of DP or DM buffer       |                                                        | 24   | 30    | 36   | kΩ |

| IOUT_0P6V               | 0.6V current capability, sink/BC1.2, DP/DM |                                                        | 250  |       |      | μΑ |

| R <sub>DP/DM_DWN</sub>  | DP/DM pull down resistance                 | source/HVDCP, DM                                       | 16   | 20    | 24   | kΩ |

| R <sub>DP/DM_LKG</sub>  | DP/DM leakage                              |                                                        | 300  | 500   | 800  | kΩ |

|                         |                                            | Slave data output high, VBUS ≥ 3.3V, data_high_sel = 0 | 3    | 3.3   | 3.6  | V  |

| VDATA_HIGH              | DP/DM data output high voltage             | Slave data output high, VBUS ≥ 3.3V, data_high_sel = 1 | 1.6  | 1.8   | 2.0  | V  |

| V <sub>DATA_LOW</sub>   | DP/DM data ouput low voltage               | Slave data output low                                  |      |       | 0.2  | V  |

| IOH_DM_3P3V             | 3.3V current capability, DM                |                                                        | 5    |       |      | mA |

|                         |                                            | dpdm_in_refh_sel = 000b                                | 0.7  | 0.8   | 0.86 | V  |

| M                       | DPDM input data rising                     | dpdm_in_refh_sel = 001b                                | 1.1  | 1.2   | 1.3  | V  |

| V <sub>IH_ТН</sub>      | threshold                                  | dpdm_in_refh_sel = 010b                                | 1.3  | 1.4   | 1.5  | V  |

|                         |                                            | dpdm_in_refh_sel = 011b                                | 1.7  | 1.8   | 1.9  | V  |

|                                    |                                           | dpdm_in_refh_sel = 100b  | 1.8   | 1.9   | 2.0   | V        |

|------------------------------------|-------------------------------------------|--------------------------|-------|-------|-------|----------|

|                                    |                                           | dpdm_in_refh_sel = 101b  | 2.0   | 2.1   | 2.2   | V        |

|                                    |                                           | dpdm_in_refh_sel = 110b  | 2.2   | 2.3   | 2.4   | V        |

|                                    |                                           | dpdm_in_refh_sel = 111b  | 2.4   | 2.5   | 2.6   | <b>V</b> |

|                                    |                                           | dpdm_in_refl_sel = 000b  | 0.5   | 0.6   | 0.7   | >        |

|                                    |                                           | dpdm_in_refl_sel = 001b  | 0.9   | 1     | 1.1   | V        |

|                                    |                                           | dpdm_in_refl_sel = 010b  | 1     | 1.1   | 1.2   | V        |

| V                                  | DPDM input data falling                   | dpdm_in_refl_sel = 011b  | 1.4   | 1.5   | 1.6   | V        |

| $V_{IL\_TH}$                       | threshold                                 | dpdm_in_refl_sel = 100b  | 1.7   | 1.8   | 1.9   | V        |

|                                    |                                           | dpdm_in_refl_sel = 101b  | 1.8   | 1.9   | 2.0   | >        |

|                                    |                                           | dpdm_in_refl_sel = 110b  | 2.1   | 2.2   | 2.3   | V        |

|                                    |                                           | dpdm_in_refl_sel = 111b  | 2.2   | 2.3   | 2.4   | V        |

| V <sub>TH_DPDMOV</sub>             | Source/DPDM OVP detection                 | DPDMOVP rising threshold | 4.6   | 4.75  | 4.9   | V        |

| 4                                  | DPDM over-voltage deglitch                | dpdm_ovp_dgl_sel = 0     |       | 4     |       | μs       |

| tdpdm_ovp                          | time                                      | dpdm_ovp_dgl_sel = 1     |       | 40    |       | μs       |

| tdata_rising                       | Data output from low to high              |                          |       | 0.3   | 1     | μs       |

| tdata_falling                      | Data output from high to low              |                          |       | 0.3   | 1     | μs       |

| tuı                                | Unit interval time                        |                          | 144   | 160   | 176   | μs       |

| tping_st                           | Adapter transmit slave ping duration time |                          | 2304  | 2560  | 2816  | μs       |

| t <sub>PING_SR</sub>               | Adapter receive master ping duration      | 5                        | 2304  | 2560  | 2816  | μs       |

| t <sub>PSR</sub> /t <sub>PST</sub> | Ping received and transmit ratio          | 1                        | 99    | 100   | 101   | %        |

| t <sub>AD</sub>                    | Terminal attach deglitch                  |                          | 450   | 500   | 550   | μs       |

|                                    | 0.7                                       | dp_to_set = 00b          | 0.475 | 0.5   | 0.525 | ms       |

| t                                  | Terminal detach deglitch                  | dp_to_set = 01b          | 0.95  | 1     | 1.05  | ms       |

| t <sub>DD</sub>                    | reminal detach degilion                   | dp_to_set = 10b          | 1.9   | 2     | 2.1   | ms       |

|                                    |                                           | dp_to_set = 11b          | 3.8   | 4     | 4.2   | ms       |

| PDO SETTING                        |                                           |                          |       |       |       |          |

| VPDO_OPEN                          | PDO1/PDO2 open voltage                    |                          |       | VDD5V |       | V        |

| 10                                 |                                           | Register programable     | 94    | 100   | 106   |          |

| INTC                               | PDO1/PDO2 bias current                    | Register programable     | 18.8  | 20    | 21.2  | μΑ       |

|                                    |                                           | Register programable     |       | 4     | 4.3   |          |

| SYSTEM CLOCK                       |                                           |                          |       |       |       |          |

| f <sub>HF_OSC</sub>                | High frequence OSC                        |                          | 22.8  | 24    | 25.2  | MHz      |

| f <sub>LF_OSC</sub>                | Low frequence OSC                         |                          | 475   | 500   | 525   | kHz      |

| GPIO PINS                          |                                           |                          |       |       |       |          |

|                                    |                                           |                          |       |       |       |          |

## SC2021A DATASHEET DRAFT

| V <sub>IH_GPIO</sub>  | Input voltage high threshold                                                                    | VBUS_PWR = 3.3V ~ 21V,<br>measured as VIO                                                  | 0.7     | V  |

|-----------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|----|

| $V_{IL\_GPIO}$        | Input voltage low threshold                                                                     | VBUS_PWR = 3.3V ~ 21V, measured as VIO                                                     | 0.3     | V  |

| V <sub>OH_GPIO</sub>  | Output high voltage                                                                             | VBUS_PWR = 6V, apply 4mA sink current from IO pin to GND externally                        | 4.5     | V  |

| $V_{\text{OL\_GPIO}}$ | Output low voltage                                                                              | VBUS_PWR = 6V, apply 10mA source current from VDD_5V to IO pin externally                  | 0.5     | V  |

| $V_{PU}$              | Pull up resistor value at GPIO pin                                                              | VBUS_PWR = 3.3V ~ 21V                                                                      | 5.1     | kΩ |

| V <sub>PD</sub>       | Pull down resistor value at GPIO pin                                                            | VBUS_PWR = 3.3V ~ 21V                                                                      | 5.1     | kΩ |

| THERMAL S             | SHUTDOWN                                                                                        |                                                                                            | Ola,    | I  |

| Ттн                   | Thermal shutdown threshold (LDO), SC2021A will reset when junction temperature is over $T_{TH}$ | T <sub>TH</sub> rising                                                                     | 160 180 | °C |

| T <sub>TH_HYS</sub>   | Over temperature hysteresis                                                                     | T <sub>J</sub> falling below T <sub>TH</sub> - T <sub>TH_HYS</sub> , SC2021A will restart. | 15      | °C |

| 1). It is recomm      | nended to set VDAC code at least 60 at 3.2                                                      | eV on VBUS.                                                                                |         | -  |

|                       |                                                                                                 | 2V on VBUS.                                                                                |         |    |

|                       |                                                                                                 | 2V on VBUS.                                                                                |         |    |

|                       |                                                                                                 | 2V on VBUS.                                                                                |         |    |

|                       | nended to set VDAC code at least 60 at 3.2                                                      | 2V on VBUS.                                                                                |         |    |

## SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

## 8 Detailed Description

## 8.1 Power Supply

SC2021A contains an internal high-voltage LDO which supports wide input range. VBUS\_PWR is the power supply input pin of internal LDO. It converts voltage on VBUS\_PWR to 5V and supplies internal modules.

For applications, VBUS\_MON should be connected to the VBUS on USB port, and VBUS\_PWR should be connected to internal VBUS node. It is recommended to place a  $1\mu$ F ceramic capacitor close to the VDD5V pin.

## 8.2 NMOS Gate Driver

The Type-C and USB PD specifications require the VBUS isolation implementation for the Type-C port. SC2021A provides NMOS gate driver to control the isolation MOSFET between the internal VBUS node and the Type-C port. The gate driver is controlled by register bit. The voltage VGS is clamp to 7V. The IC provides 4 different pull-up capabilities from  $20k\Omega$  to  $200k\Omega$  so to suit different MOSFETs.

## 8.3 VBUS Discharging Paths

The IC integrates VBUS discharging paths from VBUS\_MON VBUS\_PWR and VBUS\_A pins to ground respectively. These paths help drain the residual charge on the bulk capacitors to meet the application requirements. The typical equivalent impedance of discharge path on VBUS\_MON pin and VBUS\_A pin are  $1k\Omega$ . Discharging path on VBUS\_PWR pin is a constant current from 45mA to 150mA, which can be configured by registers. These discharge paths are activated at detachment or a lower VBUS voltage transition occurring. All discharging paths can be controlled by firmware.

#### 8.4 ADC

In the Type-C, USB PD or other quick charge applications, it is necessary to monitor the VBUS voltage and current. The SC2021A integrates a 10-bit Successive Approximation Analog to Digital Converter (SAR ADC) with a reference voltage of 2.253V at a sampling rate from 5kHz to 50kHz.

The ADC supports 10-channel input as below. For VBUS\_MON VBUS\_PWR and VBUSA, an internal ratio of 1/10 is built in. The ratio of DPDM and VDD5V channel is 1/4.

The Internal Temperature Sense (ITS) unit converts the temperature to voltage. Users can get the die temperature by sampling the channel. The ratio of voltage to temperature

is  $2.819 \text{mV/}^{\circ}\text{C}$  and the output of ITS is 733.94 mV at the temperature of  $27 ^{\circ}\text{C}$ .

Table 1. ADC input channel

| ADC_CH<br>_SEL[3:0] | Input Signal     | Note                                                       |

|---------------------|------------------|------------------------------------------------------------|

| 0000                | 1/10 x VBUS_PWR  | With 1/10 internal divider                                 |

| 0001                | 1/10 x VBUS_MON  | With 1/10 internal divider                                 |

| 0010                | VRSNS × 40 or 20 | The gain of current sense amplifier can be set as 40 or 20 |

| 0010                | 1/4 x DPx or DMx | With 1/4 internal divider                                  |

| 0100                | 1/4 x VDD5V      | With 1/4 internal divider                                  |

| 0101                | AD2              |                                                            |

| 0110                | AD1              |                                                            |

| 0111                | AD0              |                                                            |

| 1000                | ITS              | Internal temperature sense                                 |

| 1001                | 1/10 x VBUSA     | With 1/10 internal divider                                 |

## 8.5 PDO Setting

SC2021A provides two ports to support external PDO setting. The PDO pin can source a bias current and can be configured as input of ADC channel. SC2021A broadcasts different source capabilities through CC or DPDM by detecting the resistors connected to PDO pins.

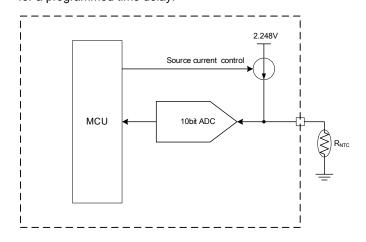

As shown in the figure, the PDO pins can be used for temperature detecting. Each of NTC pins source current on the  $R_{NTC}$ , and the voltage can be sampled by 10-bit ADC. Source current can be configured as  $100\mu A$ ,  $20\mu A$  or  $4\mu A$ . The over-temperature protection will be triggered if the voltage is below an over-temperature protection threshold for a programmed time delay.

## SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

## 8.6 CV CC Control Loop for ACDC

SC2021A contains 2 DACs and 2 error amplifiers for OPTO pin to regulate output voltage and current. For voltage regulation, VDAC is a 10-bit DAC with internal 2.048V reference voltage. SC2021A supports at least 20mV per step for VBUS output voltage regulation. The adjust time ranges from 20 µs to 250 µs which can be set by firmware.

VBUS output regulation should be as the following equation.

$$V_{REG} = 2 + VDAC \ code * 0.020$$

For example, if VDAC code = 150, the output voltage  $V_{REG} = 5V$ .

SC2021A integrates a high side current sense amplifier for constant current regulation and output current sampling. The gain of the amplifier can be configured as 40 or 20. For 3mohm application, SC2021A supports up to 8A constant current regulation.

The IDAC is 10-bit with 1.2V reference. The regulation current (IREG) is decided by IDAC code, sense resistance (RSNS) and the gain of current sense amplifier (GSNS). The relationship between these parameters should be as follows.

$$I_{REG} = \frac{IDAC\ code \times 1.2}{(2^{10} \times R_{SNS} \times G_{SNS})}$$

For example, if  $R_{SNS} = 5m\Omega$ ,  $G_{SNS} = 40$ , IDAC code = 512,  $I_{REG} = 3A$ .

## 8.7 CV CC Control Loop for DCDC

Generally, DCDC output voltage and current is controlled through the FB pin, so SC2021A integrates another set of voltage and current regulation for DCDC application.

SC2021A can source current or sink current to DCDC FB, which is equivalent to changing the voltage divider ratio of the feedback node. For voltage regulation, FBVDAC outputs voltage from 0 to 1023 mV. Each step corresponds to 1mV. Current magnitude is decided by the following equation, and direction is set by register.

$$I_{\rm FB} = \frac{V_{\rm FBVDAC}}{R_{\rm FBS}}$$

The relationship between V<sub>FBDAC</sub> and DCDC output voltage is as follows.

$$V_{\rm OUT} = \left(1 + \frac{R_{\rm UP}}{R_{\rm DWN}}\right) V_{\rm REF} - \frac{V_{\rm FBVDAC} \cdot R_{\rm UP}}{R_{\rm FBS}} \ ({\rm FB \ source \ current \ })$$

$$V_{\rm OUT} = \left(1 + \frac{R_{\rm UP}}{R_{\rm DWN}}\right) V_{\rm REF} + \frac{V_{\rm FBVDAC} \cdot R_{\rm UP}}{R_{\rm FBS}} \text{ (FB sink current )}$$

$V_{\text{REF}}$  is the reference voltage of power IC.  $R_{\text{UP}}$  and  $R_{\text{DWN}}$  are the resistor divider.  $R_{\text{FBS}}$  is the resistance between FBS pin and ground.

For current regulation, it is the same to ACDC application except the reference voltage. It is decided by the following equation.

$$I_{\text{FBREG}} = \frac{IDAC \ code \times 2.248}{(2^{10} \times R_{SNS} \times G_{SNS})}$$

For example, if  $R_{SNS} = 5m\Omega$ ,  $G_{SNS} = 40$ , IDAC code = 512, IFBREG = 5.62A.

## 8.8 DPDM Interface

The SC2021A contains 2 DPDM interfaces which can be configured as discharging out port (provider). The DPDM interfaces are available for USB-A port applications or Type-C port applications. It supports Apple-2.4A, BC1.2 DCP, HVDCP, FCP, SCP, VOOC and other proprietary fast charging protocols.

All of the DPDM pins can be configured flexible for different applications. SC2021A supports Apple-2.4A mode, which broadcasts 2.7V voltage on both DP and DM pins with 30kohm output impendence. If 2.4A mode advertisement on DPDM is enabled, it is recommended that VBUS should be able to supply at least 2.4A of current.

SC2021A can be also configured as a dedicated charging port (DCP), which complies with the BC1.2 specification. When DCP mode is enabled, SC2021A shorts DP and DM pin through a 200hm resistor.

SC2021A supports HVDCP mode for some high voltage protocols. Under HVDCP mode, DPx and DMx can check the voltage by internal comparators or detect some proprietary fast charging protocols such as SCP, UART and I2C.

#### 8.9 CC Interface

The IC can be configured as source only. It presents Rp on CC1 and CC2. CC1 and CC2 are the configuration channel pins used for connection and attachment detection, plug orientation determination and system configuration management across USB Type-C cable. Once an attachment is detected, the IC will apply VBUS voltage and broadcast source capabilities.

Current source presented on CC can be configured to  $330\mu A$ ,  $180\mu A$  and  $80\mu A$ . Each of the CC pins contains comparators to decide CC\_RD and CC\_RA attachment.

## SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

#### 8.9.1 VCONN Switch

SC2021A features a more than 50mA VCONN power with a fixed Overcurrent Protection (OCP) of 70mA.

The IC supports electronically marked cables assembly for more than 3A power delivery. By default, passive cables support up to 3A. The IC can check the cable types through internal CC comparators. If an e-marker cable is detected, the IC supplies the cable with VCONN and communicates with it to check the cable current ratings. As a consequence, source power supply advertises any PDO if cable is identified as able to sustain such current. Refer to PD specification, the IC supports up to 5A power delivery application.

When VCONN switch is turned on, SC2021A will continuously monitor current on CC pin. If VCONN output current is above 70mA, VCONN over-current flag will be set, and VCONN switch can be turned off by firmware. SC2021A supports reverse current protection on VCONN switch to avoid damage if CC pin is short to VBUS.

When VCONN switch is turned on, the IC will continuously monitor current on CC pin. VCONN over-current flag will be set if VCONN output current is above 70mA. Once VCONN OCP is triggered, VCONN switch can be turned off by firmware. The IC supports reverse current protection on VCONN switch to avoid damage if CC pin is short to VBUS.