# SLM27211 120-V, 4-A Peak, High-Frequency High-Side and Low-Side Driver

#### **GENERAL DESCRIPTION**

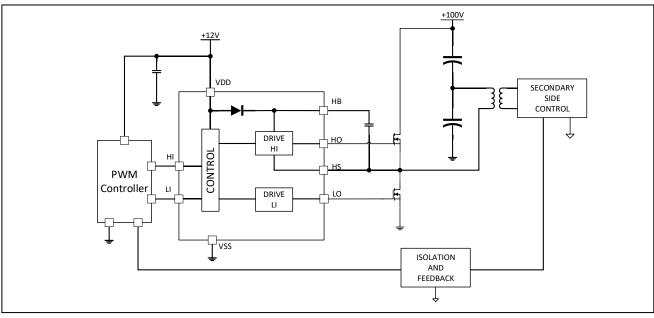

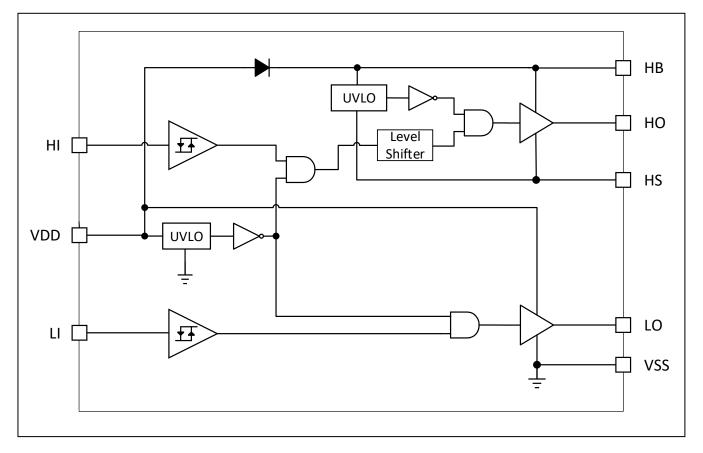

The SLM27211 is a high-frequency N-channel MOSFET driver include a 120V bootstrap diode and high-side and low-side drivers with independent inputs for maximum control flexibility. This allows for N-channel MOSFET control in half-bridge, full-bridge, two-switch forward, and active clamp forward converters. The low-side and the high-side gate drivers are independently controlled and matched to 2ns between the turn on and turn off of each other.

An on-chip bootstrap diode eliminates the external discrete diodes. Under voltage lockout is provided for both the high-side and the low-side drivers forcing the outputs low if the drive voltage is below the specified threshold.

#### **TYPICAL APPLICATIONS**

- Power supplies for telecom, Datacom, and merchant

- Half-Bridge and Full-Bridge converters

- Push-Pull converters

- High voltage synchronous-buck converters

- Two-Switch forward converters

- Active-Clamp forward converters

- Class-D audio amplifiers

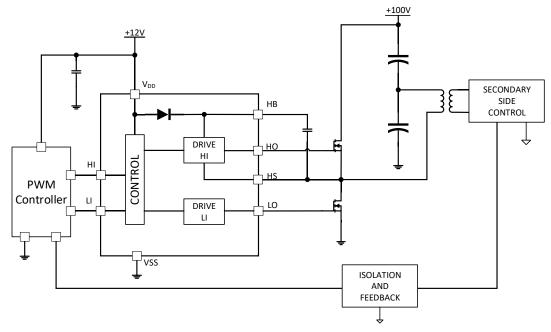

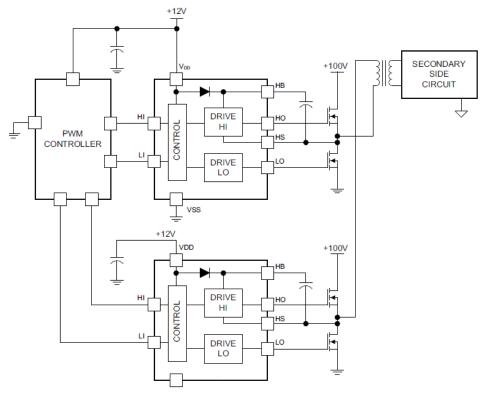

#### TYPICAL APPLICATION CIRCUIT

#### FEATURES

- Drives two N-Channel MOSFETs in high-side and low-side configuration

- Input pins are Independent of supply voltage range

- Maximum boot voltage of 120 V

- 8V to 17V VDD operation range

- 4.5A sink and 3A source output currents

- 7ns rise and 5ns fall time with1000pF load

- 22ns(typical) propagation delay time

- Under voltage lockout for high-side and lowside driver

- 2ns delay matching

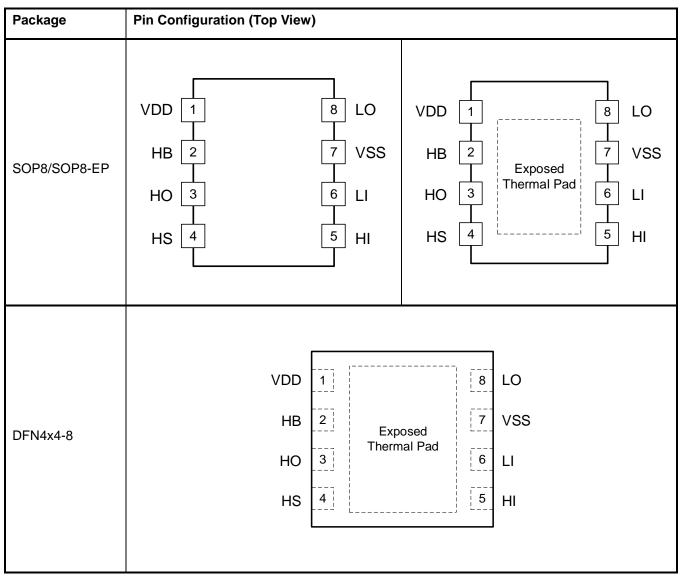

- Package options: SOP8, SOP8-EP, DFN4x4-8.

## **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| No.                           |                               |                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SOP8,<br>SOP8-EP,<br>DFN4x4-8 | Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                |  |

| 1                             | V <sub>DD</sub>               | Positive supply to the lower-gate driver. De-couple this pin to Vss (GND). Typical decoupling capacitor range is 0.22 $\mu F$ to 4.7 $\mu F.$                                                                                                                                                                                                                                              |  |

| 2                             | НВ                            | High-side bootstrap supply. The bootstrap diode is on-chip but the external bootstrap capacitor is required. Connect positive side of the bootstrap capacitor to this pin. Typical range of HB bypass capacitor is 0.022 $\mu$ F to 0.1 $\mu$ F. The capacitor value is dependent on the gate charge of the high-side MOSFET and must also be selected based on speed and ripple criteria. |  |

| 3                             | НО                            | High-side output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                                                                                                                                                                       |  |

| 4                             | HS                            | High-side source connection. Connect to source of high-side power MOSFET.<br>Connect the negative side of bootstrap capacitor to this pin.                                                                                                                                                                                                                                                 |  |

| 5                             | HI <sup>(1)</sup>             | High-side input.                                                                                                                                                                                                                                                                                                                                                                           |  |

| 6                             | LI <sup>(1)</sup>             | Low-side input.                                                                                                                                                                                                                                                                                                                                                                            |  |

| 7                             | VSS                           | Negative supply terminal for the device that is generally grounded.                                                                                                                                                                                                                                                                                                                        |  |

| 8                             | LO                            | Low-side output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                                                                                                                                                         |  |

|                               | Thermal<br>Pad <sup>(2)</sup> | Utilized on the SOP8-EP and DFN4x4-8 package only. Electrically referenced to VSS (GND). Connect to a large thermal mass trace or ground plane to dramatically improve thermal performance.                                                                                                                                                                                                |  |

(1) HI or LI input is assumed to connect to a low impedance source signal. The source output impedance is assumed less than  $100 \Omega$ . If the source impedance is greater than  $100 \Omega$ , add a bypassing capacitor, each, between HI and VSS and between LI and VSS. The added capacitor value depends on the noise levels presented on the pins, typically from 1 nF to 10 nF should be effective to eliminate the possible noise effect. When noise is present on two pins, HI or LI, the effect is to cause HO and LO malfunctions to have wrong logic outputs.

(2) The thermal pad is not directly connected to any leads of the package; however, it is electrically and thermally connected to the substrate which is the ground of the device.

### **ORDERING INFORMATION**

| Order Part No. | Package           | QTY       |

|----------------|-------------------|-----------|

| SLM27211CB-DG  | SOP8-EP, Pb-Free  | 2500/Reel |

| SLM27211CA-DG  | SOP8, Pb-Free     | 2500/Reel |

| SLM27211EK-DG  | DFN4x4-8, Pb-Free | 3000/Reel |

## FUNCTIONAL BLOCK DIAGRAM

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

|                                                                                          |                                          | Min           | Max                   | Unit |

|------------------------------------------------------------------------------------------|------------------------------------------|---------------|-----------------------|------|

| Supply voltage range, V <sub>DD</sub> <sup>(2)</sup> , V <sub>HB</sub> – V <sub>HS</sub> |                                          | -0.3          | 20                    | V    |

| Input voltages on LI and HI,                                                             | Input voltages on LI and HI, VLI, VHI    |               | 20                    | V    |

| Output voltage on LO, VLO                                                                | DC                                       | -0.3          | V <sub>DD</sub> + 0.3 |      |

|                                                                                          | Repetitive pulse < 100 ns <sup>(3)</sup> | -2            | V <sub>DD</sub> + 0.3 | V    |

| Output voltage on HO, V <sub>HO</sub>                                                    | DC                                       | Vнs – 0.3     | V <sub>нв</sub> + 0.3 |      |

|                                                                                          | Repetitive pulse < 100 ns <sup>(3)</sup> | VHS – 2       | V <sub>нв</sub> + 0.3 | V    |

| Voltage on HS, V <sub>HS</sub>                                                           | DC                                       | -1            | 120                   |      |

|                                                                                          | Repetitive pulse < 100 ns <sup>(3)</sup> | –(24 V – VDD) | 120                   | V    |

| Voltage on HB, V <sub>HB</sub>                                                           |                                          | -0.3          | 120                   | V    |

| Operating virtual junction temperature range, $T_J$                                      |                                          | -40           | 150                   | °C   |

| Storage temperature, T <sub>STG</sub>                                                    |                                          | -65           | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to VSS unless otherwise noted. Currents are positive into and negative out of the specified terminal.

(3) Verified at bench characterization. VDD is the value used in an application design.

#### **ESD RATINGS**

| Symbol | Definition | Value | Unit |

|--------|------------|-------|------|

| Vesd   | НВМ        | ±2000 | V    |

|        | CDM        | ±1000 | ·    |

### THERMAL RESISTANCE

| Package  | θ <sub>JA</sub> | Unit |

|----------|-----------------|------|

| SOP8     | 111.8           | °C/W |

| SOP8-EP  | 41.1            | °C/W |

| DFN4x4-8 | 37.7            | °C/W |

# **RECOMMENDED OPERATION CONDITIONS**

All voltages are with respect to Vss; currents are positive into and negative out of the specified terminal.

| Symbol          | Definition                                          | Min                  | Nom | Max                   | Unit |

|-----------------|-----------------------------------------------------|----------------------|-----|-----------------------|------|

| V <sub>DD</sub> | Supply voltage range on VDD                         | 8                    | 12  | 17                    | V    |

| V <sub>BS</sub> | Voltage between HB and HS                           | 8                    | 12  | 17                    | V    |

| V <sub>HS</sub> | Voltage on HS                                       | -1                   |     | 105                   | V    |

| VHS             | Voltage on HS, $V_{HS}$ (repetitive pulse < 100 ns) | –(24 V – VDD)        |     | 110                   | V    |

| V <sub>HB</sub> | Voltage on HB                                       | V <sub>HS</sub> + 8, |     | V <sub>HS</sub> + 17, | V    |

| V HB            | voltage on the                                      | V <sub>DD</sub> – 1  |     | 115                   | v    |

|                 | Voltage slew rate on HS                             |                      |     | 50                    | V/ns |

| TJ              | Operating junction temperature                      | -40                  |     | 125                   | °C   |

# STATIC ELECTRICAL CHARACTERISTICS

$V_{DD} = V_{HB} = 12 \text{ V}, V_{HS} = V_{SS} = 0 \text{ V}$ , no load on LO or HO,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Symbol             | Parameter                                | Test Condition                                           | Min  | Тур   | Max  | Unit |

|--------------------|------------------------------------------|----------------------------------------------------------|------|-------|------|------|

| SUPPLY             | CURRENTS                                 |                                                          |      |       |      |      |

| I <sub>DD</sub>    | V <sub>DD</sub> quiescent current        | V(LI) = V(HI) = 0 V                                      | 0.08 | 0.115 | 0.15 | mA   |

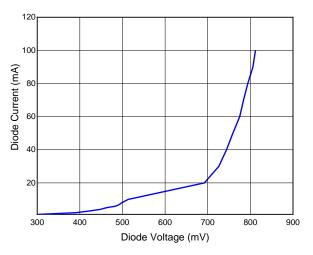

| Iddo               | VDD operation current                    | f = 500 kHz, C <sub>LOAD</sub> = 0                       | 0.7  | 1.0   | 1.5  | mA   |

| I <sub>HB</sub>    | Boot voltage quiescent current           | V(LI) = V(HI) = 0 V                                      | 0.07 | 0.095 | 0.12 | mA   |

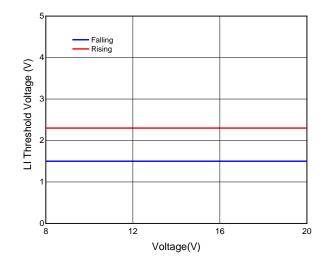

| I <sub>HBO</sub>   | Boot voltage operating current           | $f = 500 \text{ kHz}, C_{LOAD} = 0$                      | 0.7  | 0.96  | 1.2  | mA   |

| I <sub>HBS</sub>   | HB to V <sub>SS</sub> quiescent current  | V(HS) = V(HB) = 115 V                                    |      | 0.02  | 1    | μA   |

| I <sub>HBSO</sub>  | HB to Vss operating current              | f = 500 kHz, C <sub>LOAD</sub> = 0                       |      | 0.15  | 0.5  | mA   |

| INPUT              |                                          |                                                          |      |       |      |      |

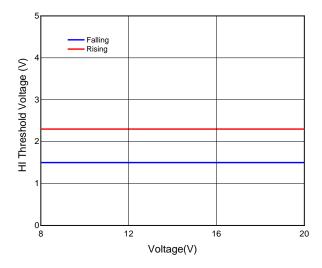

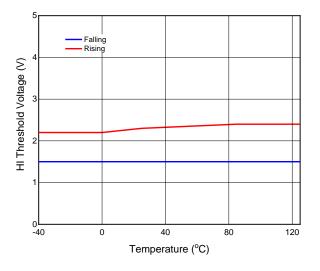

| V <sub>HIT</sub>   | Input voltage threshold                  |                                                          | 1.9  | 2.3   | 2.6  | V    |

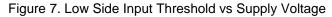

| V <sub>LIT</sub>   | Input voltage threshold                  |                                                          | 1.3  | 1.6   | 1.9  | V    |

| V <sub>IHYS</sub>  | Input voltage hysteresis                 |                                                          |      | 700   |      | m\   |

| R <sub>IN</sub>    | Input pulldown resistance                |                                                          |      | 55    |      | kΩ   |

| UNDER-             | VOLTAGE LOCKOUT (UVLO)                   |                                                          |      |       |      |      |

| V <sub>DDR</sub>   | V <sub>DD</sub> turn on threshold        |                                                          | 6.4  | 7     | 7.7  | V    |

| V <sub>DDHYS</sub> | Hysteresis                               |                                                          |      | 0.5   |      | V    |

| V <sub>HBR</sub>   | V <sub>HB</sub> turn on threshold        |                                                          | 5.7  | 6.7   | 7.7  | V    |

| V <sub>HBHYS</sub> | Hysteresis                               |                                                          |      | 1.1   |      | V    |

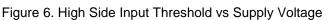

| BOOTST             | RAP DIODE                                |                                                          |      |       |      |      |

| VF                 | Low-current forward voltage              | I <sub>VDD-HB</sub> = 100 µА                             |      | 0.4   | 0.7  | V    |

| V <sub>FI</sub>    | High-current forward voltage             | I <sub>VDD-HB</sub> = 100 mA                             |      | 0.82  | 0.95 | V    |

| RD                 | Dynamic resistance, $\Delta VF/\Delta I$ | $I_{VDD-HB} = 100 \text{ mA} \text{ and } 80 \text{ mA}$ | 0.8  | 1.0   | 1.2  | Ω    |

| LO GATE            | E DRIVER                                 |                                                          |      |       |      |      |

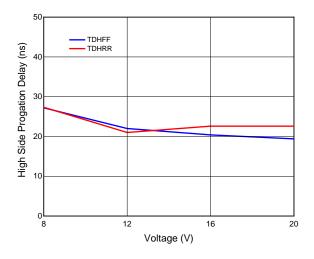

| V <sub>LOL</sub>   | Low-level output voltage                 | I <sub>LO</sub> = 100 mA                                 | 0.04 | 0.08  | 0.18 | V    |

| V <sub>LOH</sub>   | High level output voltage                | $I_{LO} = -100 \text{ mA}, V_{LOH} = V_{DD} - V_{LO}$    | 0.12 | 0.18  | 0.25 | V    |

| I <sub>SRC_L</sub> | Peak pull-up current <sup>(1)</sup>      | V <sub>LO</sub> = 0 V                                    |      | 3     |      | A    |

| Isnk_l             | Peak pull-down current <sup>(1)</sup>    | V <sub>LO</sub> = 12 V                                   |      | 4.5   |      | A    |

| HO GAT             | E DRIVER                                 |                                                          |      |       | 1    |      |

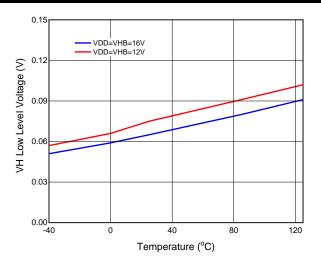

| V <sub>HOL</sub>   | Low-level output voltage                 | Iно = 100 mA                                             | 0.04 | 0.08  | 0.18 | V    |

| V <sub>HOH</sub>   | High-level output voltage                | $I_{HO} = -100 \text{ mA}, V_{HOH} = V_{HB} - V_{HO}$    | 0.12 | 0.18  | 0.25 | V    |

| Isrc_h             | Peak pull-up current <sup>(1)</sup>      | V <sub>HO</sub> = 0 V                                    |      | 3     |      | A    |

| Isnk_h             | Peak pull-down current <sup>(1)</sup>    | V <sub>HO</sub> = 12 V                                   |      | 4.5   |      | A    |

(1) Ensured by design.

Sillumin Semiconductor Co., Ltd. - www.sillumin.com

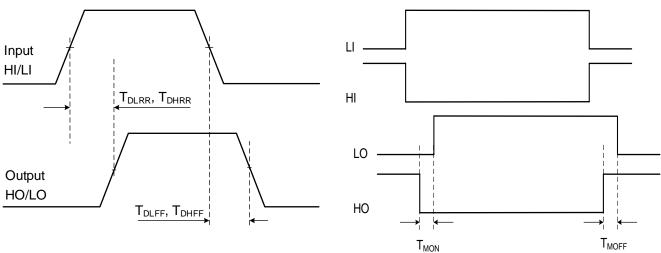

# SWITCHING CHARACTERISTICS

$T_A = 25^{\circ}C$ , unless otherwise noted.

| Symbol                                            | Parameter                                          | Test Conditions                                      | Min | Тур  | Max | Unit |

|---------------------------------------------------|----------------------------------------------------|------------------------------------------------------|-----|------|-----|------|

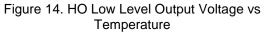

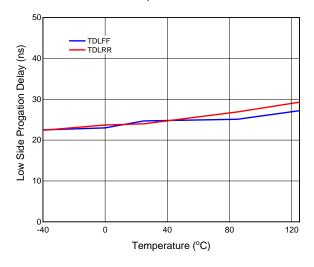

| T <sub>DLFF</sub>                                 | $V_{\text{LI}}$ falling to $V_{\text{LO}}$ falling |                                                      | 18  | 22   | 30  | ns   |

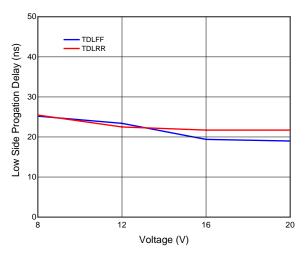

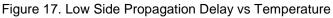

| T <sub>DHFF</sub>                                 | $V_{\text{HI}}$ falling to $V_{\text{HO}}$ falling |                                                      | 18  | 22   | 30  | ns   |

| T <sub>DLRR</sub>                                 | $V_{\text{LI}}$ rising to $V_{\text{LO}}$ rising   | C <sub>LOAD</sub> = 0                                | 17  | 21   | 29  | ns   |

| T <sub>DHRR</sub>                                 | $V_{\text{HI}}$ rising to $V_{\text{HO}}$ rising   |                                                      | 17  | 21   | 29  | ns   |

| T <sub>MON</sub>                                  | From HO OFF to LO ON                               |                                                      |     | 2    | 7   | ns   |

| T <sub>MOFF</sub>                                 | From LO OFF to HO ON                               |                                                      |     | 2    | 7   | ns   |

| t <sub>R</sub>                                    | LO rise time                                       | $C_{LOAD} = 1000 \text{ pF}$ , from 10% to 90%       |     | 7    |     | ns   |

| t <sub>R</sub>                                    | HO rise time                                       |                                                      |     | 7    |     | ns   |

| t⊧                                                | LO fall time                                       | $C_{LOAD} = 1000 \text{ pF}$ , from 90% to 10%       |     | 5    |     | ns   |

| t⊧                                                | HO fall time                                       |                                                      |     | 5    |     | ns   |

| t <sub>R</sub>                                    | LO, HO                                             | $C_{LOAD} = 0.1 \ \mu\text{F}, (3 \ V \ to \ 9 \ V)$ |     | 0.35 | 0.5 | μs   |

| t⊧                                                | LO, HO                                             | $C_{LOAD} = 0.1 \ \mu F$ , (9 V to 3 V)              |     | 0.16 | 0.3 | μs   |

| Minimum input pulse width that changes the output |                                                    | ges the output                                       |     |      | 50  | ns   |

| Bootstrap diode turn off time (1)(2)              |                                                    | $I_F = 20 \text{ mA}, I_{REV} = 0.5 \text{ A}^{(3)}$ |     | 20   |     | ns   |

(1) Ensured by design.

(2)  $I_{F}$ : Forward current applied to bootstrap diode,  $I_{REV}$ : Reverse current applied to bootstrap diode.

(3) Typical values for  $T_A = 25^{\circ}C$ .

8

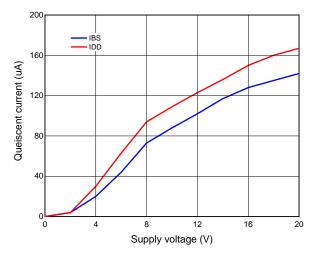

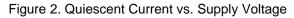

# TYPICAL PERFORMANCE CHARACTERISTICS

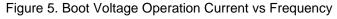

Figure 4. IDD Operation Current vs. Frequency

Sillumin Semiconductor Co., Ltd. – <u>www.sillumin.com</u> **Rev1.0,May, 2022**

Figure 3. Diode Current vs Diode Voltage

# SLM27211

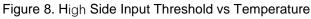

Figure 10. Rising Threshold Voltage vs Temperature

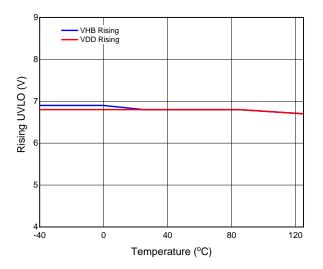

Figure 12. HO High Level Output Voltage vs Temperature

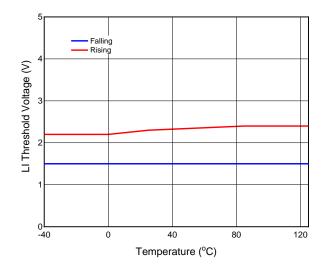

Figure 9. Low Side Input Threshold vs Temperature

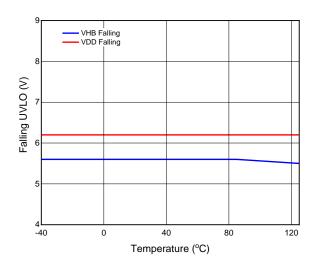

Figure 11. Falling Threshold Voltage vs Temperature

# SLM27211

Figure 16. Low Side Propagation Delay vs Voltage

Figure 18. High Side Propagation Delay vs Voltage

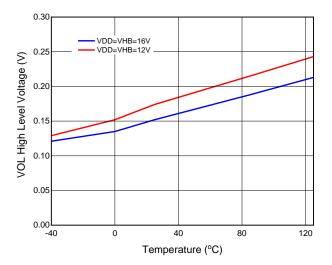

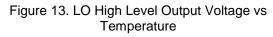

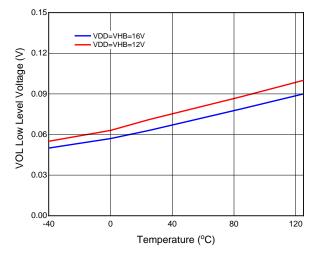

Figure 15. LO Low Level Output Voltage vs Temperature

Figure 19. High Side Propagation Delay vs Temperature

## **DEVICE FUNCTIONAL MODES**

The device operates in normal mode and UVLO mode. In the UVLO mode, the output (HO and LO) both hold low. In the normal mode the output state is dependent on states of the HI and LI pins. Table 2 lists the output states for different input pin combinations.

#### Table 2. Device Logic Table

| HI PIN | LI PIN | HO <sup>(1)</sup> | LO <sup>(2)</sup> |

|--------|--------|-------------------|-------------------|

| L      | L      | L                 | L                 |

| L      | Н      | L                 | Н                 |

| Н      | L      | Н                 | L                 |

| Н      | Н      | Н                 | Н                 |

(1) HO is measured with respect to HS.

(2) LO is measured with respect to VSS.

## **APPLICATION INFORMATION**

To affect fast switching of power devices and reduce associated switching power losses, a powerful gate driver is employed between the PWM output of controllers and the gates of the power semiconductor devices. Also, gate drivers are indispensable when it is impossible for the PWM controller to directly drive the gates of the switching devices. With the advent of digital power, this situation will be often encountered because the PWM signal from the digital controller is often a 3.3V logic signal which cannot effectively turn on a power switch. Level shifting circuitry is needed to boost the 3.3V signal to the gate drive voltage (such as 12 V) in order to fully turn on the power device and minimize conduction losses. Traditional buffer drive circuits based on NPN/PNP bipolar transistors in totem-pole arrangement, being emitter follower configurations, prove inadequate with digital power because they lack level-shifting capability. Gate drivers effectively combine both the level-shifting and buffer-drive functions. Gate drivers also find other needs such as minimizing the effect of high-frequency switching noise by locating the high-current driver physically close to the power switch, driving gate-drive transformers, and controlling floating power-device gates, reducing power dissipation and thermal stress in controllers by moving gate charge power losses from the controller into the driver.

### POWER DISSIPATION

Power dissipation of the gate driver has two portions as shown in Equation 1.

$$P_{DISS} = P_{DC} + P_{SW}$$

(1)

The DC portion of the power dissipation is  $P_{DC} = I_Q \times VDD$  where  $I_Q$  is the quiescent current for the driver. The quiescent current is the current consumed by the device to bias all internal circuits such as input stage, reference voltage, logic circuits, protections, and also any current associated with switching of internal devices when the driver output changes state (such as charging and discharging of parasitic capacitances, parasitic shoot-through, and so forth). The SLM27211 features very low quiescent currents and contain internal logic to eliminate any shoot-through in the output driver stage. Thus, the effect of the  $P_{DC}$  on the total power dissipation within the gate driver can be safely assumed to be negligible. The power dissipated in the gate-driver package during switching (Psw) depends on the following factors:

- Gate charge required of the power device (usually a function of the drive voltage VG, which is very close to input bias supply voltage V<sub>DD</sub>)

- Switching frequency

- Use of external gate resistors. When a driver device is tested with a discrete, capacitive load calculating the power that is required from the bias supply is fairly simple. The energy that must be transferred from the bias supply to charge the capacitor is given by Equation 2.

$$EG = \frac{1}{2} \times C_{LOAD} \times V_{DD}^2$$

Sillumin Semiconductor Co., Ltd. – <u>www.sillumin.com</u>

(2)

Here,  $C_{\text{LOAD}}$  is load capacitor and  $V_{\text{DD}}$  is bias voltage feeding the driver

There is an equal amount of energy dissipated when the capacitor is charged and when it is discharged. This leads to a total power loss given by Equation 3.

$$PG = C_{LOAD} \times V_{DD}^{2} \times f_{SW}$$

Here, fsw is the switching frequency

The switching load presented by a power MOSFET/IGBT is converted to an equivalent capacitance by examining the gate charge required to switch the device. This gate charge includes the effects of the input capacitance plus the added charge needed to swing the drain voltage of the power device as it switches between the ON and OFF states. Most manufacturers provide specifications of typical and maximum gate charge, in nC, to switch the device under specified conditions. Using the gate charge Qg, determine the power that must be dissipated when switching a capacitor which is calculated using the equation  $Q_G = C_{LOAD} \times V_{DD}$  to provide Equation 4 for power.

$$P_G = C_{LOAD} \times V_{DD}^2 \times f_{SW} = Q_G \times V_{DD} \times f_{SW}$$

This power  $P_G$  is dissipated in the resistive elements of the circuit when the MOSFET/IGBT is being turned on and off. Half of the total power is dissipated when the load capacitor is charged during turn on, and the other half is dissipated when the load capacitor is discharged during turn off. When no external gate resistor is employed between the driver and MOSFET/IGBT, this power is completely dissipated inside the driver package. With the use of external gate-drive resistors, the power dissipation is shared between the internal resistance of driver and external gate resistor.

### POWER SUPPLY RECOMMENDATIONS

The bias supply voltage range for which the SLM27211 device is recommended to operate is from 8 V to 17 V. The lower end of this range is governed by the internal under voltage-lockout (UVLO) protection feature on the V<sub>DD</sub> pin supply circuit blocks. Whenever the driver is in UVLO condition when the VDD pin voltage is below the supply start threshold (V<sub>DDR</sub>), this feature holds the output low, regardless of the status of the inputs. The upper end of this range is driven by the 20V absolute maximum voltage rating of the VDD pin of the device (which is a stress rating). Keeping a 3V margin to allow for transient voltage spikes, the maximum recommended voltage for the V<sub>DD</sub> pin is 17 V. The UVLO protection feature also involves a hysteresis function, which means that when the V<sub>DD</sub> pin bias voltage has exceeded the threshold voltage and device begins to operate, and if the voltage drops, then the device continues to deliver normal functionality unless the voltage drop exceeds the hysteresis specification V<sub>DDHYS</sub>. Therefore, ensuring that, while operating at or near the 8V range, the voltage ripple on the auxiliary power supply output is smaller than the hysteresis specification of the device is important to avoid triggering device shutdown. During system shutdown, the device operation continues until the V<sub>DD</sub> pin voltage has exceeded the V<sub>DDR</sub>, which must be accounted for while evaluating system shutdown timing design requirements. Likewise, at system start-up the device does not begin operation until the V<sub>DD</sub> pin voltage has exceeded the V<sub>DDR</sub> threshold.

The quiescent current consumed by the internal circuit blocks of the device is supplied through the VDD pin. Although this fact is well known, it is important to recognize that the charge for source current pulses delivered by the LO pin is also supplied through the same VDD pin. As a result, every time a current is sourced out of the LO pin, a corresponding current pulse is delivered into the device through the VDD pin. Thus, ensure that a local bypass capacitor is provided between the VDD and VSS pin and located as close to the device as possible for the purpose of decoupling. A low-ESR, ceramic surface-mount capacitor is required. Sillumin recommends using a capacitor in the range 0.22  $\mu$ F to 4.7  $\mu$ F between VDD and VSS. In a similar manner, the current pulses delivered by the HO pin are sourced from the HB pin. Therefore, a local decoupling capacitor is needed between the HB and HS pins and its value depends on the external MOSFET or IGBT used and the switching frequency.

(3)

(4)

# **TYPICAL APPLICATION**

Figure 20. SLM27211 Typical Application Circuit in Half Bridge

Figure 21. SLM27211 Typical Application Circuit in Full Bridge

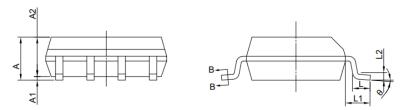

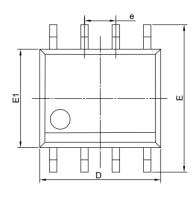

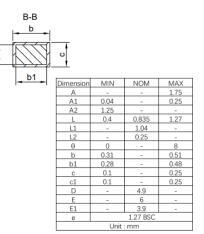

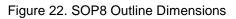

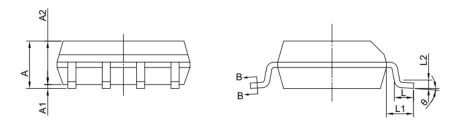

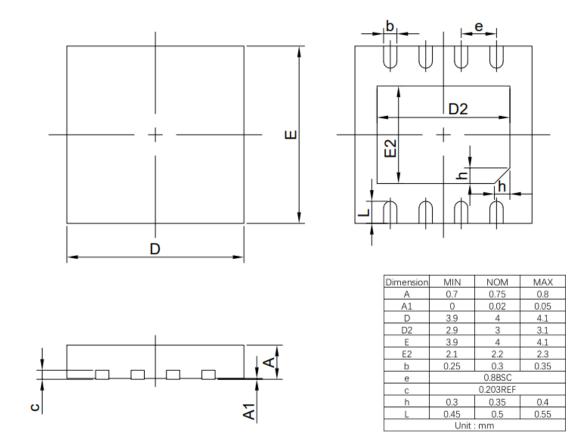

## PACKAGE CASE OUTLINES

5

Figure 24. DFN4x4-8 Outline Dimensions

# **REVISION HISTORY**

Note: page numbers for previous revisions may differ from page numbers in current version

| Page or Item                    | Subjects (major changes since previous revision) |  |

|---------------------------------|--------------------------------------------------|--|

| Rev 1.0 Datasheet, 2022-05-05   |                                                  |  |

| Whole document Initial released |                                                  |  |